作者:电子创新网张国斌

台积电(中国) 总经理罗镇球

目前,随着摩尔定律放缓,Chiplet成为延续摩尔定律的不二选择,尤其是随着Chiplet产业联盟的成立,这个技术更是炙手可热,笔者发现凡是今年的半导体研讨会基本都有Chiplet的话题讨论,那Chiplet技术的未来将由哪些公司来主导?是半导体IC大厂还是晶圆代工厂抑或是封测厂?在最近召开的2023中国半导体设计年会上(ICCAD2023),电子创新网等多家媒体专访了台积电(中国) 总经理罗镇球,他就这个技术的发展以为2024年产业发展发表了自己的观点。

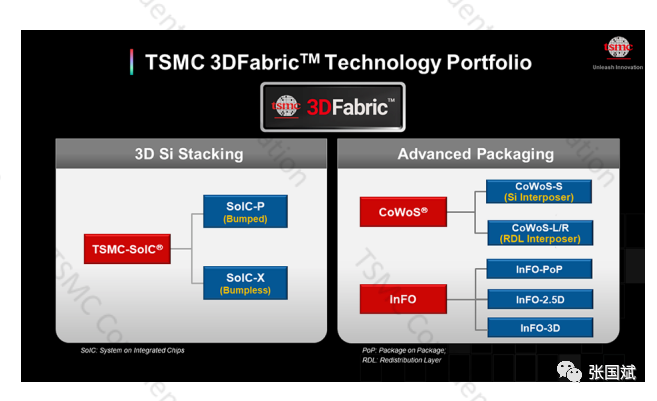

“谈到Chiplet,我们台积电从2011年推出来chip on wafer on substrate,我们到现在已经批量生产总共有12年了,第一个2.5D的西芯片就是2011年推出的,多年来,我们一直不断的在精进我们的技术,即集成的die越来越大,放进去的IC越来越多。现在大家把Chiplet叫小芯片,它实际上不能叫小芯片,因为我们在Chiplet里面看到的通通是大芯片,如果不是大芯片,不会用Chiplet,这是必然的。”他表示,“对台积电而言,我们最大的工作是提供一个健康且公平的平台,所以我们不会倾斜于在任何企业上,我们也不太想主导某个东西,我们只是觉得我们建立一个平台,一起去发展,这样对这个行业是最健康、最好的。”根据今年6月台积电研讨会公布的信息来看,目前台积电3DFabric 系统整合技术包括各种先进的 3D 芯片堆叠和先进封装技术,以支持广泛的下一代产品:在 3D 芯片堆叠方面,台积电在系统整合芯片(TSMC-SoIC®)技术家族中加入微凸块的 SoIC-P,以支持更具成本敏感度的应用。台积电的2.5D CoWoS 平台得以实现先进逻辑和高频宽记忆体的整合,适用于人工智能、机器学习和数据中心等 HPC 应用;整合型扇出层叠封装技术(InFOPoP)和 InFO-3D 支持移动应用,InFO-2.5D 则支持 HPC 小芯片整合。台积电基于堆叠芯片技术的系统整合芯片(SoIC)现可被整合于整合型扇出(InFO)或 CoWoS 封装中,以实现最终系统整合。

罗镇球强调从2011年推出第一个2.5D芯片到现在,前面很多年的研发都是赔钱在做,不过台积电一直坚信这个方向是对的,所以持续的投入,不仅有CoWoS,还推出了InFO-3D和SOIC等,这个大方向绝对是对的。

在ICCAD主题演讲中,罗镇球透露台积电每年花300亿美金做资本支出,有超过8000位研发人员,单单去年台积电在研发上的支出就超过55亿美金。这笔巨大的投入包含布局两个方面:一是2D平面式微缩推进到3D的整合,除了在芯片上的晶体管开始从平坦式变成立体式之外,封装部分也把它变成了3D;二是提升能源使用效率(Energy Efficient Performance,EEP),通过调整晶体管结构,使用新材料、新封装,甚至调整设计架构和算法,再搭配整个软件的合作,才能提升EEP指标。

“从2005年至今,每2年整个行业EEP可以提升3倍。在同样功能的芯片之下,如今使用的芯片能源消耗可能只是两年前的1/3,这是整个行业共同努力的结果。”罗镇球说。展望2024产业未来,他表示台积电确实看到景气复苏的迹象--在一些手机的供应商,还有一些消费类产品的供应商上,确实有看到,包含手机,4G、5G的手机,IoT、电视,确实有复苏的迹象。“但是绝大部分的客户,以及客户的客户都被过去一年的库存吓到了,所以现在大概没有人愿意办库存,现在看到的订单是急单,平常我们要三个月交货了,他说你两个月要给我,所以很显然他的客户也是手上没货了才找他拿。短时间之内,第一,库存的消化已经改善,已经变好,但是客户对消费者的信心不够,我们在外面的环境也能够看得到,目前在中国、全世界碰到最大的问题是消费者的信心不足,要攒一些钱留着以后花或者留本,不再像过去这样积极消费,这是最根本的问题。”他指出,“我相信整个半导体行业往上走,会持续高速的发展,短期的波动是过去三年疫情期间大家抢货之后的后遗症,你抢货抢得越久,库存就要去化的越久,所以大概现在已经去化了差不多一年了。”罗镇球还特别指出:“我觉得任何一个行业它的进入门槛高就表示它的价值非常高,而且它的重要性会很高,半导体行业是精英聚集的地方,现在最红的公司是英伟达、AMD,各位回想十年前的AMD在做什么?它在地上被英特尔摩擦,而英伟达呢?差点因为某个订单而倒掉,半导体行业就是自由竞争,大家要各凭本事努力,所以新创公司绝对要有信心,只要你好好的干,你肯定可以变成拳王。不过很重要的是,当了拳王之后绝对不可以放松,要想办法让自己连任拳王。”

注:本文为原创文章,未经作者授权严禁转载或部分摘录切割使用,否则我们将保留侵权追诉的权利