单个企业从试点团队到数百名工程师规模部署,一场芯片设计领域的智能化变革正在发生。

今日,领先的AI芯片设计解决方案提供商兆源软件宣布,其革命性的芯片前端设计与验证全流程AI平台已在某行业领先客户处实现大规模生产部署。该客户已将平台从最初的试点团队扩展至数百名工程师的规模使用,日均处理数十亿tokens的工程设计数据。

这一里程碑标志着AI驱动的芯片设计工具已成功跨越产品与市场契合度的关键验证阶段。

01 SemiSeek®平台重塑芯片设计与验证流程

传统芯片设计流程中,工程师需要与分散的工具链、高昂成本和落后工作流程作斗争。兆源软件的AI平台通过统一的智能体AI架构,自动化处理从规格定义到RTL代码生成的关键任务。

SemiSeek®平台在前端设计阶段展现出显著优势,能够将原本需要数周的工作缩短至数分钟。智能体AI无缝整合进芯片设计全流程,从规格导入到波形分析,真正实现了对这一复杂多步骤流程的创新突破。针对数万行代码能够在不到半小时内完成设计与满足流片要求的验证,而传统方法需要数周时间。

02 从试点到大规模部署的产品演化路径

SemiSeek®平台最初在该客户的一个试点团队中投入使用。平台迅速证明了其价值,帮助工程师将验证效率较行业常规方案提升80%。

随着平台价值的显现,部署规模迅速扩大。目前,该客户已将平台扩展至数百名工程师的日常使用,以日均处理数十亿tokens的规模运行。这一增长轨迹印证了AI EDA工具的发展趋势——通过AI技术实现对芯片设计流程的优化和自动化。

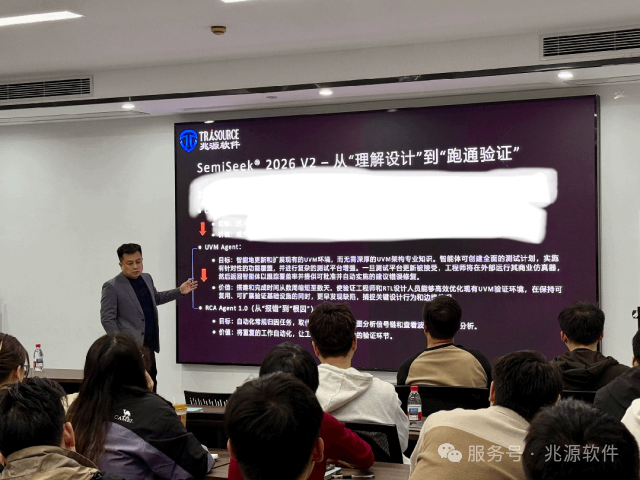

03 新版本功能强化DV自动化能力

在今日的客户现场交流活动中,兆源软件展示了其新版本平台的增强功能。工程师可以使用自然语言描述设计需求,系统自动生成符合规范的代码。在验证环节,SemiSeek®平台中的智能体智能地更新和扩展现有的UVM环境,而无需深厚的UVM架构专业知识。智能体可创建全面的测试计划,实施有针对性的功能覆盖,并进行复杂的测试平台增强。一旦测试平台更新被接受,将自动运行其商业仿真器,然后返回智能体以跟踪覆盖率并提供可批准并自动实施的建议错误修复。同时自动化常规归因任务,取代人工依据设计意图分析信号链和查看波形进行根因分析。将重复的工作自动化,让工程师专注于复杂的验证环节。

04 市场前景与行业影响

AI在EDA领域的应用正迅速成熟。行业巨头如Synopsys、Cadence和西门子EDA均已推出各自的AI驱动工具。但兆源软件SemiSeek®多智能体平台采用AI原生重新构想芯片设计与验证流程,并非简单的传统EDA+AI,从而更大的提高整体流程的效率。

据业内报告指出,到2030年,单个芯片中集成的晶体管数量将达到1万亿,芯片设计复杂性呈指数级增长。与此同时,全球半导体工程师短缺问题日益突出,到2024年,中国半导体行业人才缺口高达23万人。兆源软件的解决方案通过大幅提高设计效率,为缓解行业人才压力提供了可行路径。公司创始人兼CEO表示:“2026年半导体领域的AI正从试验阶段转向关键任务基础设施。赢家将是那些深度集成、尊重现有工作流程并能带来可衡量生产力提升的平台。”

这一创新也使中国芯片设计企业获得了差异化竞争能力,可快速响应细分市场对定制化芯片的需求。

随着今日产品路线图的发布,兆源软件计划进一步扩大市场渗透。公司表示,目前已有近10家领先半导体企业部署了其平台。

AI与EDA的深度融合正在重新定义芯片设计的基本规则,为半导体行业带来更加广阔的发展空间,引领行业迈向一个全新的智能时代。

来源:兆源软件