作者:电子创新网张国斌

11月2日,一年一度的技术盛会2023 国际集成电路展览会暨研讨会(IIC Shenzhen)在深圳召开,在主题为“科技向善,半导体赋能”的全球CEO峰会上,多位中外半导体公司的CEO/CTO等从宏观角度畅谈了半导体产业的热点话题。

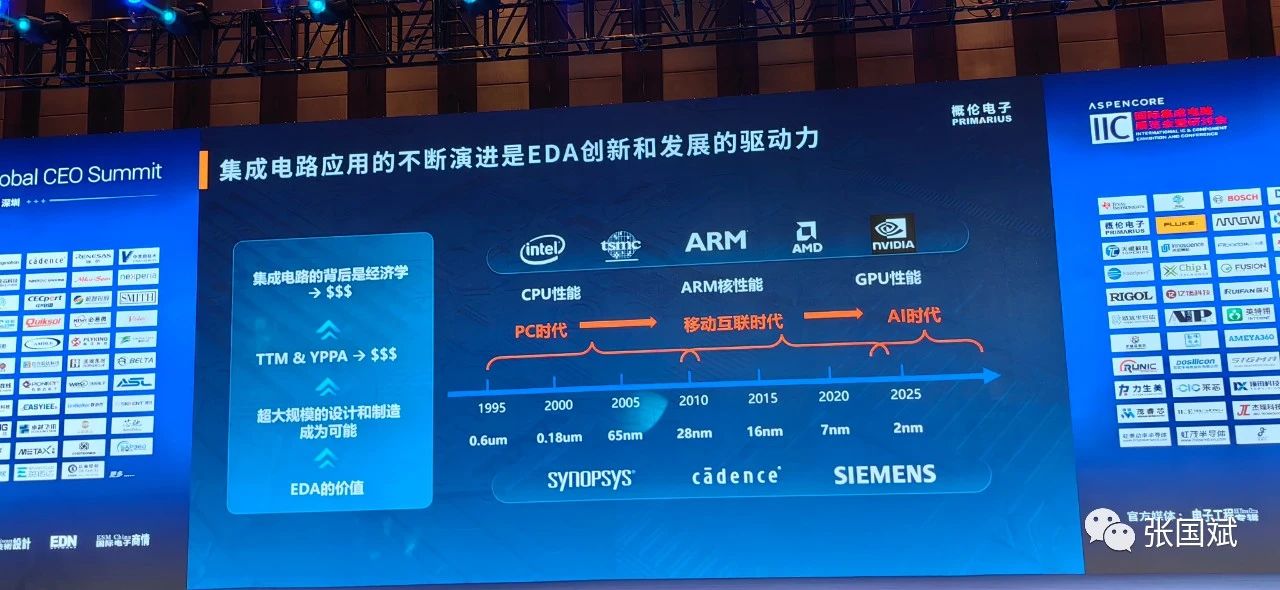

概伦电子董事兼总裁杨廉峰博士发表了题为《融合创新,以EDA赋能存储芯片全定制设计流程》的演讲,在演讲中,他指出:从过去30年的发展,从早期的PC时代到移动互联,包括现在的人工智能。其实EDA是要支撑终端应用,比如早期CPU的性能,每年都看英特尔发什么样的CPU。后来看ARM,每一个工艺节点,现在要看GPU的算力。在这个过程中,EDA发挥了支撑的作用,EDA的发展也是被这些应用反过来驱动的。

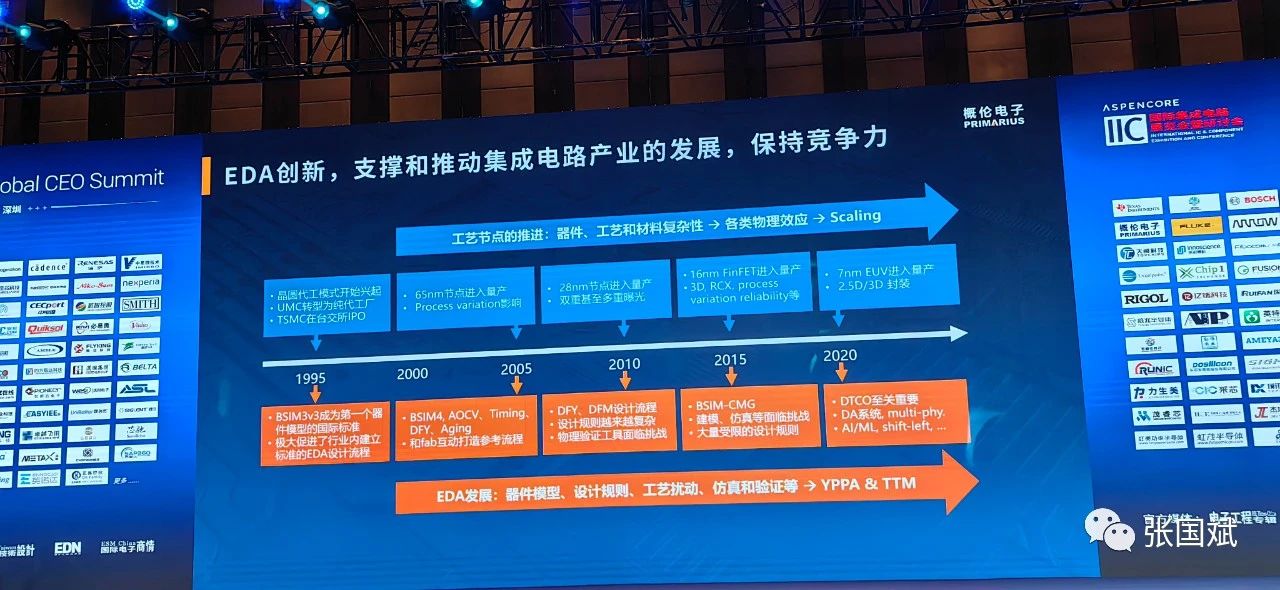

“谈到EDA的价值,大家认为EDA是用来做设计或者制造。EDA的第一个表面的价值是让我们的超大规模设计和制造成为可能,但是它背后真正EDA能发挥价值,是让我们的芯片设计,芯片能够有竞争力,包括上市的时间,包括良率、可靠性、性能等。我们认为摩尔规律背后是经济学的规模。EDA要跟产业一起成长,要承载帮助产品的设计和制造,能够有竞争力。”他强调,“在过去的30年当中,首先EDA要能支撑摩尔定律的推进,从各个工艺节点,从1995年开始,TSMC代工的模式进入到行业的主流,特别进入到65纳米的工艺节点,工艺的漂移成比较重要的因素,到后面每一个工艺节点的问题,都需要EDA去表征,每个环节都需要EDA去表征,能够去描述,同时能够更高效地去解决、分析、验证问题。在这个过程中,最终的目标是希望通过EDA能支撑工艺节点的推进,能够去处理和应对器件工艺和材料的复杂性,能够处理各种物理效应,从而能够帮助我们的设计,能够在相对比较短的时间去达成芯片所需要的良率、性能。”

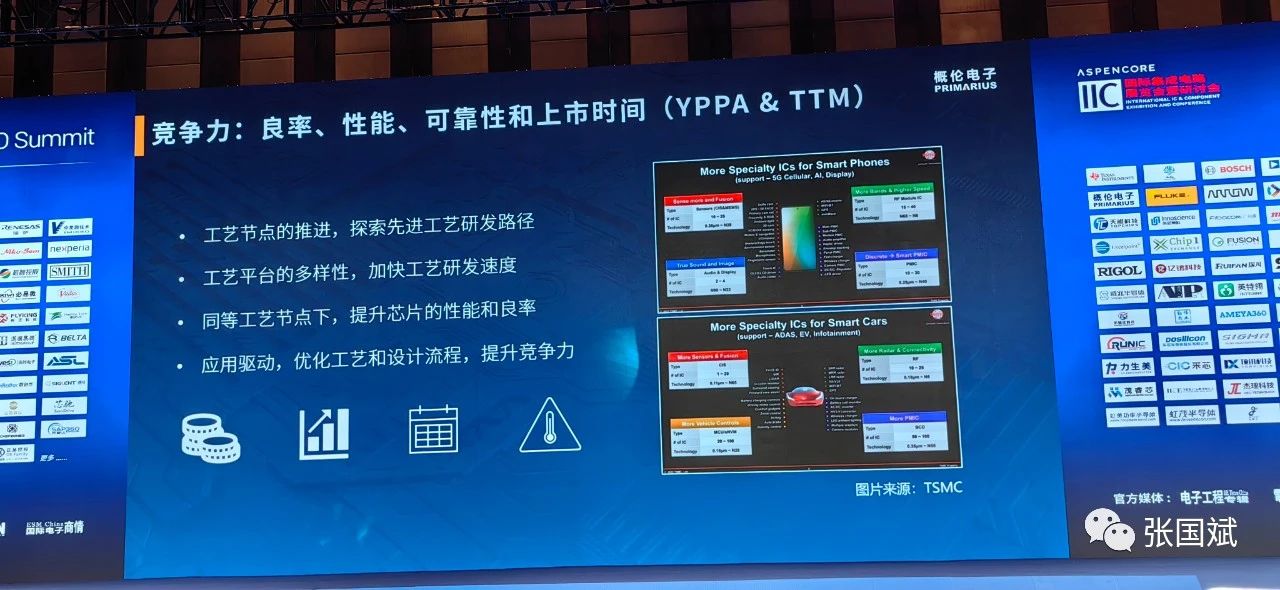

他特别指出:在当前中国有些工艺节点受限的情况下,怎么实现在同等工艺节点,提升性能和良率。包括是否通过特定的应用,优化设计流程,提升芯片竞争力。这些都是EDA在为设计和制造提供支撑过程中,能够去确保的工作,这也是EDA价值的体现。

他认为从EDA的角度看,从90纳米、65纳米往下,早期的摩尔定律这个阶段结束了。现在业界是希望把工艺平台的开发和设计以及它们之间的互动能够通过方法学联动起来。所以DTCO的方法学是推动摩尔定律的推进,以及帮助产品在新的工艺节点下提升竞争力。

他指出在工艺推进到5纳米、3纳米以下之后,因为器件的缩微变得越来越困难,现在很多要考虑先进封装,所以现在有一个词叫STCO,就是把先进封装,包括工艺平台开发和芯片设计、系统设计集成在一起,规划考虑去优化,这也是能持续保持摩尔定律继续有效,是集成电路这个行业持续推进,能保持经济学的规律持续推进的手段。

|DTCO是工艺节点推进和提升芯片竞争力的EDA方法学

他表示概伦电子成立13年来一直沿着DTCO的方法学推进一些核心技术、流程的研发。DTCO主要要考虑从工艺开发和设计之间的接口,所以在工艺开发和设计之间的接口环节,概伦电子做了很多工作。基于这样的基础,概伦电子的目标是希望加速从工艺平台开发到新设计之间迭代的过程,更重要的是通过快速的迭代,能够优化最终产品的性能或者是良率。

“这样的技术手段,在过去工业界,像IDM公司是比较容易实现的。可是在代工厂这样的商业模式下,这样的工作不是特别容易做的。所以就需要EDA厂商在中间起到桥梁的作用,帮助设计公司能够更好地把工艺潜力挖掘出来,或者是帮助工艺开发的用户,针对特定的应用,把工艺平台更好地优化,最终产品能有更好的良率和性能。”他指出,“从这个角度来讲,我们也提供了一些完整的解决方案,包括从软件,从服务,包括整个平台,这里面就包括了器件的特定测试,有了特定测试之后,大家知道晶体管是整个芯片最基础的单元,所以晶体管的模型是整个EDA分析和仿真验证最基础的单元。所以晶体管模型不管是射频特性的模型建立,包括噪声特性、可靠性特性等等,都是EDA仿真分析的基础。基于这样的电学特性的建模,可以把它的一些物理特性,比如PDK,能够建设起来,同时能够再上升到单元层级,帮助客户把标准单元或者一些定制单元能够进行定制开发和优化,最终上升到IP的环节。所以整个流程对工艺开发到设计之间的流程是最关键的接口环节,这个环节在过去十多年,帮助了国内所有的芯片到先进工艺,以及一些领先的设计公司去挖掘工艺的潜力,这方面做了很多工作。工艺平台的转移需要做这些工作,这方面的经验我们也积累了很多。这也可以帮助客户在工艺和设计之间的优化,能够进一步取得更好的工作。”

| 助力高端存储器、IC设计

他表示除了在工艺平台开发和工艺设计之间的桥梁外,概伦电子在设计流程方面也做了一些工作。

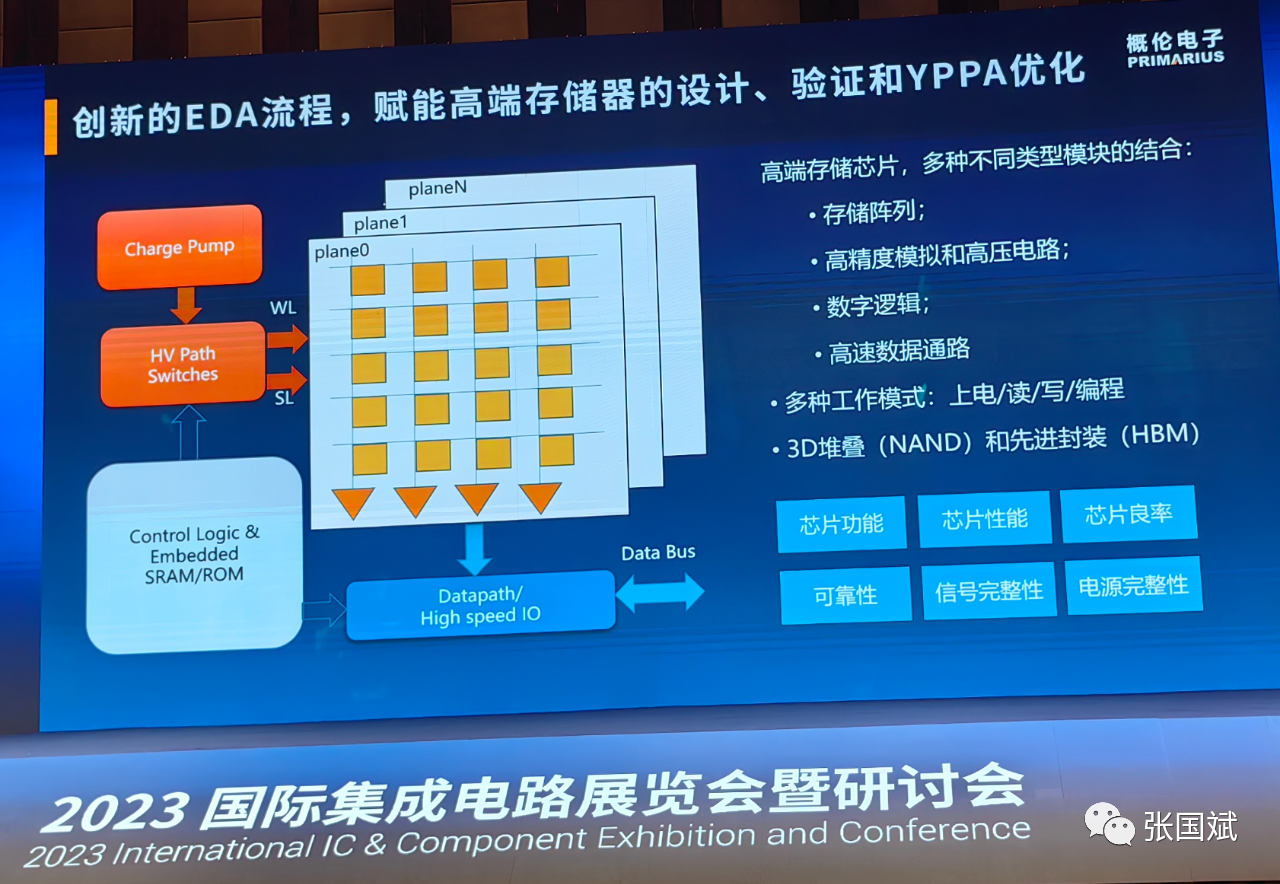

一个比较典型的案例就是存储器,对于高端存储器,里面包括了不同类型的电路组合,包括存储阵列、高压电路、数字逻辑、高速数据通道。要处理这样高端的存储器芯片,需要覆盖到不同类型的电路处理,包括不同的工作模式,以及在高端的存储器的先进封装、3D堆叠、3D堆叠的HBM、或者NAND的工作。

概伦电子需要考虑验证和优化功能和性能以及良率,这是一些基础的指标。包括在可靠性,包括信号完整性,电源完整性的要求,这个是从设计角度的要求。如果按过去传统流程需要一个个去做,现在如果有可能跟工艺做一些迭代,在基于DTCO的理念下,可以有一些创新的流程。

他说所有分析的技术要基于仿真和验证的引擎,这就是概伦电子过去13年积累打造出一体化快速电路仿真和验证平台NanoSpice,目前有国际国内领先的存储器和公司作为主力的仿真工具在使用,也能支持5纳米3纳米的工艺节点,包括所有核心的仿真,也包括了混合信号,包括了数字仿真,所以它可以支持最广泛的一些应用领域,包括存储、模拟、定制的数字逻辑电路、数模混合电路、定制数字电路。这是目前国内完整的仿真平台。

他表示基于这样的仿真验证平台,概伦电子对于设计流程也做了一些创新,希望通过设计流程的创新,能够把迭代的效率、设计的效率提升。

他还指出概伦电子标用了五六年时间,一直在推动打造一个最快的单元库,概伦电子原生支持ARM的多线程,这对ARM来讲是最好的应用场景。同时,概伦电子也和国内的云供应商如阿里云等一起合作,提供基于公有云或者私有的快速解决方案。它的最大优势是可以在单元库特征化或者定制的工作当中,特别对于现在一些先进工艺,包括做汽车电子、AI的CPU,如果对于一些库做定制时则可以提供快速的解决方案。

2021年,概伦电子并购了韩国一家EDA公司的解决方案,它可以针对数字电路做一些关键路径的提取、关键路径高精度的分析,这样可以帮助公司在先进工艺对数字电路的分析,如果在精度提高的情况下,要求比较高,特别对一些关键路径,结合概伦电子已有的仿真器的优势,帮助数字电路的客户提供更好的解决方案。

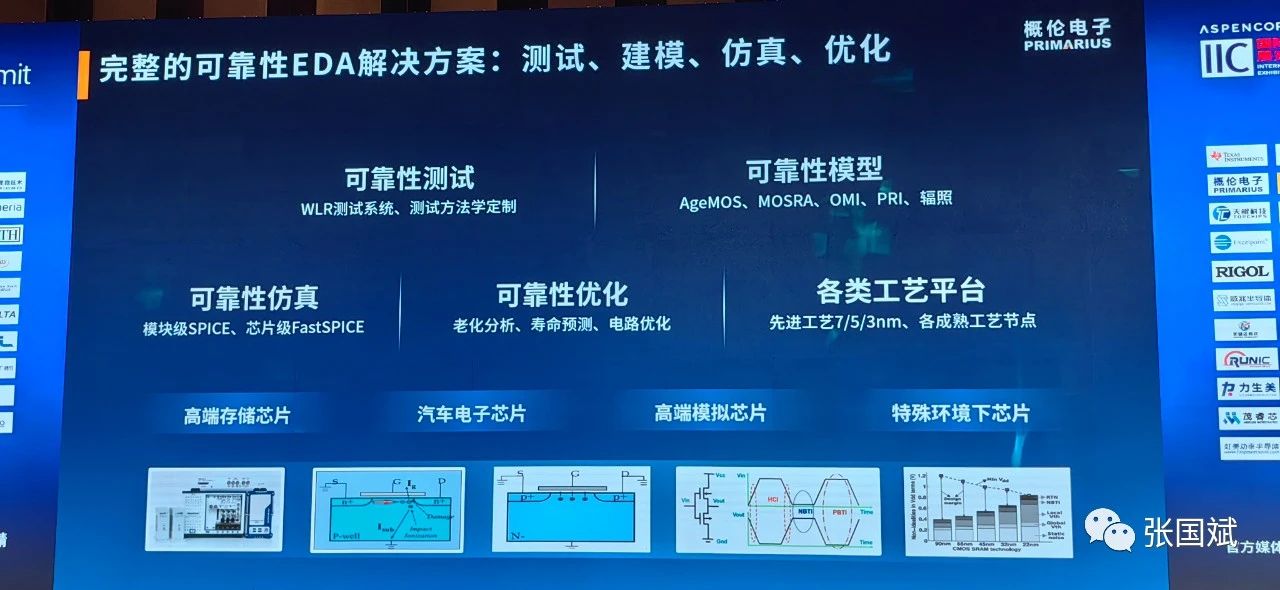

他表示概伦电子可以提供完整的可靠性的测试,包括测试系统,可靠性的测试方法学,因为可靠性测试是最耗时间的,对于一个晶体管来讲,要测到它的可靠性特性,我们要看到它降低10%的特性,可能要测十几个小时。完整的一套可靠性模型的建立需要一些创新的测试系统和测试方法学,所以概伦电子提供可靠性测试系统以及可靠性模型,包括业界常见的模型以及自研的模型。

在可靠性特性完成之后,对于整个芯片级,还要关注信号完整性,特别是先进封装,以高端存储器来为例,例如比较热门的3D堆叠,很多时候芯片完整性是必须要关注的,概伦电子也提供了完整的信号完整性解决方案,---国际大厂也在用,需要快速的瞬态分析,最终把它放在一起去评估眼图,包括特性,这对于仿真的效率和精度要求非常高。

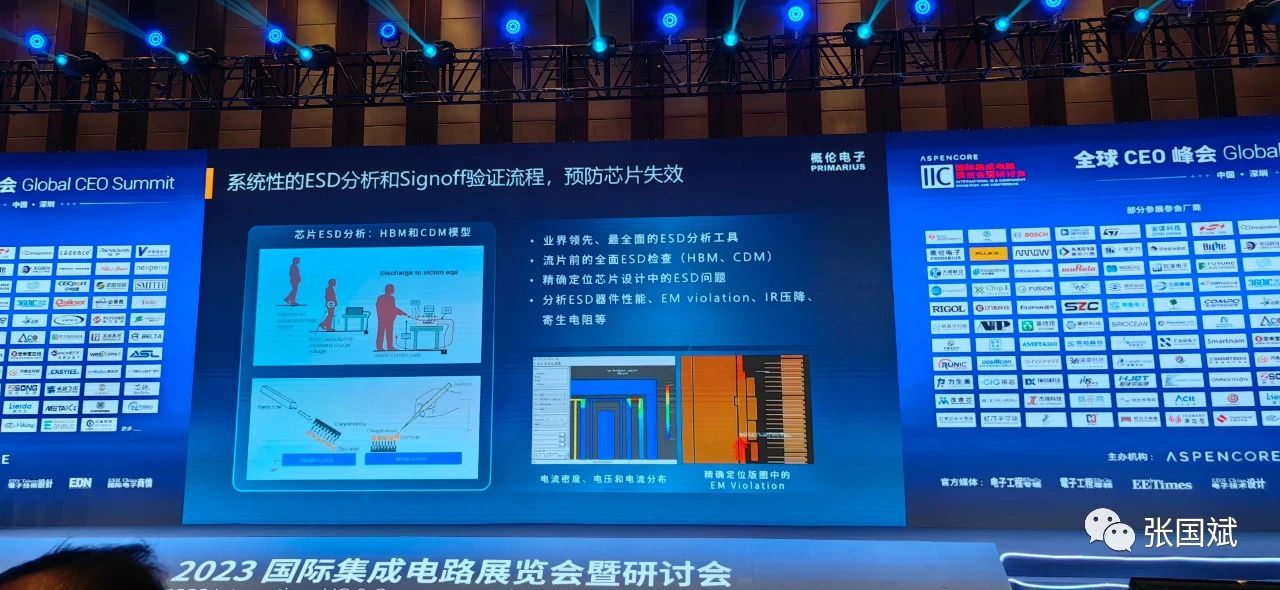

他强调在芯片封装之后,也需要关注失效机制,例如ESD。一两个月前概伦电子并购了一家比利时的EDA公司,这家公司也是做了十几年关于ESD方面的工具。它的工作是希望在流片前,帮助客户在流片前的板图做全面的检查,包括HBM、CDM的模型,最后精确定位芯片当中的问题,包括ESD器件性能、EM violation、IP压降、寄成电阻等问题。

他强调:在过去的13年,概伦电子致力于联动设计制造,希望把设计与制造两个环节联动做得更好,也是呼吁一起建设国产的EDA生态。

“EDA过去三年太热了,我们认为中国现在有很多新的应用,特别在新的形势下,会驱动中国的集成电路生态建设一个自我生态,同时跟全球的生态形成联动。我们也认为,在中国这个特殊环境下,中国的EDA也能走出自己的一条创新路。概伦电子也希望能参与,推动、建设我们自己的生态。”他指出。

注:本文为原创文章,未经作者授权严禁转载或部分摘录切割使用,否则我们将保留侵权追诉的权利